## **ASiKS-Engineering**

## **User Manual**

# **SmartLIN-RS232 HS Module**

**Document Reference No.: UM128724**

Version 1.0

Issue Date: 2019-01-15

This document provides detailed information about ASiKS-Engineering's SmartLIN-RS232 HS Module.

ASiKS-Engineering

Your Reliable Partner

in System Engineering, Prototyping, Hardware and Software Development

Dr. Andreas Schramm

Pointenweg 3, 94110 Wegscheid, Germany Tel.: +49(0)8165/4093868

E-Mail: info@asiks-engineering.com Web: https://www.asiks-engineering.com

| 1 Introduction                                | 3 |

|-----------------------------------------------|---|

| 2 Terminal Contacts                           | 3 |

| 3 Interface Detection                         | 3 |

| 4 Communication                               | 4 |

| 4.1 RS232 Port Initialization (UART protocol) | 4 |

| 4.2 LIN Bus Data Sending                      | 4 |

| 4.3 LIN Bus Data Receiving                    | 5 |

| 5 Disclaimer                                  | 5 |

| 6 Contact Information                         | 5 |

| Appendix A – Revision History                 | 4 |

#### 1 Introduction

The SmartLIN-RS232 HS Module shown in Figure 1 is used for easily connecting a LIN Bus to the serial Port (RS232) of e.g. a PC.

As it is an active interface, LIN Bus specific signals like synchronisation break and synchronisation delimiter are generated by the interface and hence no special algorithm is required by the host application.

Figure 1: SmartLIN-RS232 HS Module

This interface provides the following features:

- Standard DIN rail housing with 8 terminal contacts

- Dimensions: 64mm x 64mm x 18mm

## 2 Terminal contacts

Table 1 illustrates the electrical characteristics of the SmartLIN-RS232 HS Module's terminal contacts.

| Clamp | Symbol | Description               | Min  | Тур | Max    | Unit |

|-------|--------|---------------------------|------|-----|--------|------|

| Α     | TxD*   | RS232 data input          |      |     |        |      |

| В     | RxD*   | RS232 data output         |      |     |        |      |

| С     | DTR*   | RS232 signal input        |      |     |        |      |

| D     | CTS*   | RS232 signal output       |      |     |        |      |

| E     | RTS*   | RS232 signal input        |      |     |        |      |

| F     | GND    | Power Ground              | 0    | 0   | 0      | V    |

| G     | VBat   | Battery supply            | 8    | 12  | 16     | V    |

| Н     | LIN**  | LIN bus line input/output | -0.3 |     | VBat+1 | V    |

Table 1: Electrical characteristics

Note \*: The electrical characteristics of the RS232 Standard apply.

Note \*\*: Master configuration (1k PullUp), slave configuration on request

#### 3 Interface Detection

The SmartLIN-RS232 HS Module simply can be checked for availability as follows:

- RTS and DTR of the RS232 communication port are set and cleared again

- CTS is monitored

- If CTS is "ON", the interface is detected correctly and ready for use

Listing 1 illustrates a programming example of an interface detection routine.

```

[...]

EscapeCommFunction(serial_struct_info->pComPortFile,SETDTR);

EscapeCommFunction(serial_struct_info->pComPortFile,SETRTS);

EscapeCommFunction(serial_struct_info->pComPortFile,CLRDTR);

EscapeCommFunction(serial_struct_info->pComPortFile,CLRRTS);

GetCommModemStatus(serial_struct_info->pComPortFile,&dwModemState);

```

Listing 1: Interface detection source code example

#### 4 Communication

## 4.1 RS232 Port Initialization (UART protocol)

The host's communication port needs to be configured as follows:

Baud rate: user defined

Data Bits: 8Parity: NoneStop Bits: 1

## 4.2 LIN Bus Data Sending

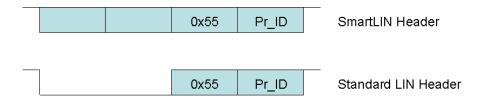

The SmartLIN-RS232 HS Module handles the LIN synchronisation break and delimiter generation whereby no special baud rate conversion mechanism is required by the host application. The LIN message header simply is expanded by some trailing bytes replacing the LIN synchronisation break and delimiter as illustrated in Figure 2.

Figure 2: SmartLIN-RS232 LIN header structure

The values for synch break and delimiter easily can be calculated using the SmartLIN Bit Time Tool, available for download at our homepage.

**NOTE:** Depending on the delimiter value, RTS wire needs to be set or cleared accordingly!

**NOTE:** The communications port's DTR wire **needs to be toggled** any time a message (Header and as the case may be response) is sent by the host application!

## 4.3 LIN Bus Data Receiving

For receiving of LIN Bus data using the SmartLIN-RS232 HS Module, the host application needs to monitor the "CE\_BREAK" (communication break) flag through what the start of new LIN Bus Header is indicated.

#### 5 Disclaimer

For damage of any kind, arising by the employment of the SmartLIN-RS232 HS Module, no requirements can be made valid opposite the supplier!

#### **6 Contact Information**

ASiKS-Engineering Dr. Andreas Schramm Pointenweg 3 94110 Wegscheid Germany

Tel: +49(0)8165/4093868

E-mail: info@asiks-engineering.com

Web Site URL https://www.asiks-engineering.com

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. ASiKS-Engineering will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document.

## Appendix A – Revision History

Revision History 1.0 Initial Release 15<sup>th</sup> January 2019